虽然DDS工作频点接近直流,但根据奈奎斯特原理,其比较高频率只能到时钟频率的一半。虽然可以工作在高于奈奎斯特区,但是性能下降非常快。另一个严重的问题是由于DDS技术中固有的许多因素导致的较高杂散,例如数位截取、量化和DAC转换误差。DSS的形式可以是完全集成的芯片或可以使用单独的现场可编程门阵列(FPGA)和DAC芯片来实现。后者可将数字部分限制在FPGA内部,因此隔离了EMI引起的杂散。如今FPGA有足够的能力来建立相当复杂的多核相位累加器和索引表,由数位截取导致的杂散电平可忽略不计。结果主要的杂散源通常是由于DAC的非线性和量化噪声引起的。频率综合器可以操作在非常宽的频带范围内,通常从几百MHz到数GHz。湖南低噪声频率综合器模块

频率综合器一直是通讯、雷达系统中的重要组成部分。频率综合器的小型化和高性能是目前的研究趋势。相较于传统封装技术,系统级封装技术(SiP,SysteminPackage)能够更好地满足现代产品对电子封装小型化的要求。多物理场耦合分析可以对体积减小带来的多物理场间的耦合效应进行预测,从而指导设计,提高设计可靠性。微波射频信号的感知、接收和处理要求接收系统具有高分辨率、抗电磁干扰和大带宽等性能,以应对高密集度和复杂度的电磁环境。传统基于电子学的射频信号感知和接收系统面临着带宽窄、高频高损、频响不平坦和电磁干扰严重等诸多电子瓶颈,越来越难以满足高频宽带信号接收的需求。深圳1kHz频率综合器推荐厂家频率综合器具有很高的频率稳定性,即使在温度变化、振荡器老化或其他环境变化的情况,输出频率能保持稳定。

射频/微波行业一直致力于提供更高性能、更强功能、更小尺寸、更低功耗和更低成本的频率综合器。尽管所有的频率综合器由于各自具体应用不同,呈现差异,但是他们的基本设计目标相同。理想的频率综合器比较好是宽带的,拥有良好的频率分辨率,适用于多种潜在应用。频率综合器的特性在很大程度上取决于其特殊架构,可以被分成几个主要的类型,如图2所示。直接频率综合架构是直接从获得的参考信号中创建输出信号,通过在频域控制和组合参考信号(直接模拟综合),或通过在时域构造输出波形(直接数字综合)间接频率综合方法假定输出信号以一种输出频率和输入参考信号相关的形式(例如,锁相)在频率综合器内部生成。同样,间接频率综合可以用模拟和数字技术来完成。然而实际的综合器为了得到多种技术的各自优势,通常是结合多种技术的混合设计。

本振频率调节范围取决于分频系数的变化范围,准确地说,取决于分频器的位数,由于位数是任意的(理论上),所以频率调节范围相当宽,也就是可预选的电视频道相当多。频率合成式高频头能兼容接收CATV有线增补频道,不过,要在CPU的控制数据中增加CATV增补频道所需的频道数据才行。这些必须要在CPU的软件设计中由生产厂家事先设定,一般用户及检修人员无法改变。频率合成技术还广泛应用于手机的发射电路、本振电路中,这里不再具体分析,有兴趣的读者可参考相关书籍。频率综合器非常适合需要高性能和低抖动的应用,例如高速数据通信和精密测量。

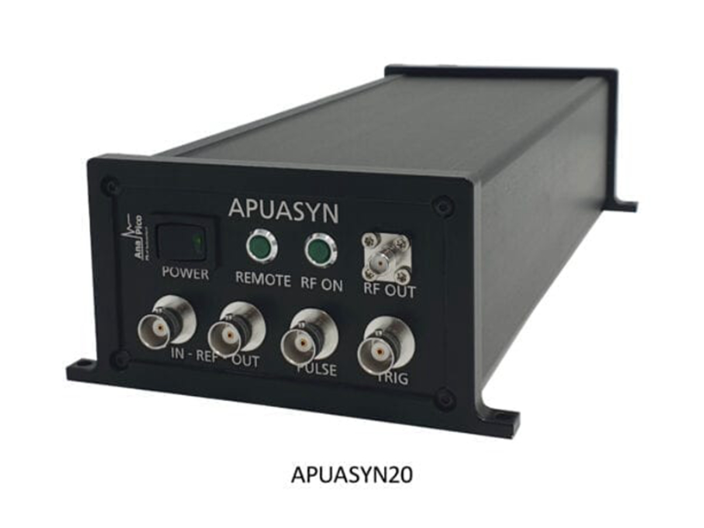

DDS是另一个产生良好的频率分辨率的有效解决方案,且没有通常的鉴相器频率下降问题。DDS具有良好的频率分辨率,用于高频参考频率或作为小数分频器。虽然DDS提供了良好的频率分辨率,但其杂散水平通常很高。此外由于PLL的乘法机制,进一步恶化了杂散。虽然两种方案看起来不同,但是它们对DDS杂散的影响方式相同。在这两种情况下,总的环路分频系数由VCO输出和鉴相器比较频率之间的比率决定。可以利用许多技术减少DDS杂散,例如使用可调时钟(如上述的小数N综合器)或如图5所示将其上变频后再将DDS信号进行分频。注意上变频相关的DDS带宽减少,往往需要根据所需的特定的频率规划进一步扩展。这可以通过多种方法实现,例如,利用可调(相对固定)分频系数。 AnaPico宽带频率综合器输出范围分别覆盖8kHz至20GHz、22GHz和40GHz,分辨率低至0.00001Hz。浙江简单易操作频率综合器哪家好

频率综合器模块通常用于无线电、通信、雷达、卫星导航、测试测量等领域中。湖南低噪声频率综合器模块

一个简单的PLL频率综合器表现出各种限制和权衡。对频率综合器性能的主要影响是由为了实现较高的频率所需的大分频比和较高的分辨率引起的。注意由PLL器件产生的任何噪声以20logN的速度恶化,其中N为分频比。工作在小步长的传统的整数分频锁相环,分频比较大是因为步长必须等于鉴相器的比较频率。结果相位噪声大幅恶化。此外频率综合器的切换速度由其环路带宽决定,因此受限于鉴相器比较频率。由于环路滤波器带外抑制不足,或者甚至环路不稳定,增加环路带宽可能会导致更高频的参考杂散。因此,这个简单的单环架构锁相环受限于相互排斥的设计目标。它通常用于要求不高的应用领域或侧重于低成本应用。湖南低噪声频率综合器模块