在晶圆键合技术的设备适配性研究中,科研团队分析现有中试设备对不同键合工艺的兼容能力,提出设备改造的合理化建议。针对部分设备在温度均匀性、压力控制精度上的不足,团队与设备研发部门合作,开发了相应的辅助装置,提升了设备对先进键合工艺的支持能力。例如,为某型号键合机加装的温度补偿模块,使晶圆表面的温度偏差控制在更小范围内,提升了键合的均匀性。这些工作不仅改善了现有设备的性能,也为未来键合设备的选型与定制提供了参考,体现了研究所对科研条件建设的重视。围绕第三代半导体器件需求,研究晶圆键合精度对器件性能的影响。山西晶圆级晶圆键合代工

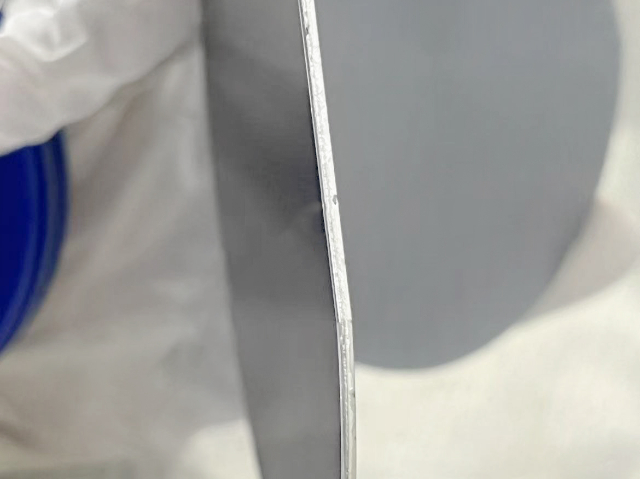

针对晶圆键合过程中的气泡缺陷问题,科研团队开展了系统研究,分析气泡产生的原因与分布规律。通过高速摄像技术观察键合过程中气泡的形成与演变,发现气泡的产生与表面粗糙度、压力分布、气体残留等因素相关。基于这些发现,团队优化了键合前的表面处理工艺与键合过程中的压力施加方式,在实验中有效减少了气泡的数量与尺寸。在 6 英寸晶圆的键合中,气泡率较之前降低了一定比例,明显提升了键合质量的稳定性。这项研究解决了晶圆键合中的一个常见工艺难题,为提升技术成熟度做出了贡献。东莞共晶晶圆键合工艺晶圆键合为虚拟现实系统提供高灵敏触觉传感器集成方案。

晶圆键合通过分子力、电场或中间层实现晶圆长久连接。硅-硅直接键合需表面粗糙度<0.5nm及超洁净环境,键合能达2000mJ/m²;阳极键合利用200-400V电压使玻璃中钠离子迁移形成Si-O-Si共价键;共晶键合采用金锡合金(熔点280℃)实现气密密封。该技术满足3D集成、MEMS封装对界面热阻(<0.05K·cm²/W)和密封性(氦漏率<5×10⁻¹⁴mbar·l/s)的严苛需求。CMOS图像传感器制造中,晶圆键合实现背照式结构。通过硅-玻璃混合键合(对准精度<1μm)将光电二极管层转移到读out电路上方,透光率提升至95%。键合界面引入SiO₂/Si₃N₄复合介质层,暗电流降至0.05nA/cm²,量子效率达85%(波长550nm),明显提升弱光成像能力。

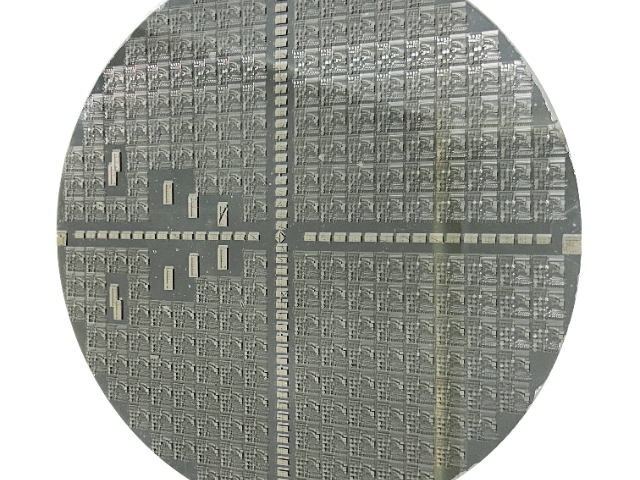

研究所针对晶圆键合技术的规模化应用开展研究,结合其 2-6 英寸第三代半导体中试能力,分析键合工艺在批量生产中的可行性。团队从设备兼容性、工艺重复性等角度出发,对键合流程进行优化,使其更适应中试生产线的节奏。在 6 英寸晶圆的批量键合实验中,通过改进对准系统,将键合精度的偏差控制在较小范围内,提升了批次产品的一致性。同时,科研人员对键合过程中的能耗与时间成本进行评估,探索兼顾质量与效率的工艺方案。这些研究为晶圆键合技术从实验室走向中试生产搭建了桥梁,有助于推动其在产业中的实际应用。晶圆键合推动高效水处理微等离子体发生器的电极结构创新。

研究所利用多平台协同优势,对晶圆键合后的器件可靠性进行多维评估。在环境测试平台中,键合后的器件需经受高低温循环、湿度老化等一系列可靠性试验,以检验界面结合的长期稳定性。科研人员通过监测试验过程中器件电学性能的变化,分析键合工艺对器件寿命的影响。在针对 IGZO 薄膜晶体管的测试中,经过优化的键合工艺使器件在高温高湿环境下的性能衰减速率有所降低,显示出较好的可靠性。这些数据不仅验证了键合工艺的实用性,也为进一步优化工艺参数提供了方向,体现了研究所对技术细节的严谨把控。晶圆键合推动人工视觉芯片的光电转换层高效融合。河北直接晶圆键合加工工厂

晶圆键合推动自发光量子点显示的色彩转换层高效集成。山西晶圆级晶圆键合代工

针对晶圆键合过程中的表面预处理环节,科研团队进行了系统研究,分析不同清洁方法对键合效果的影响。通过对比等离子体清洗、化学腐蚀等方式,观察晶圆表面的粗糙度与污染物残留情况,发现适当的表面活化处理能明显提升键合界面的结合强度。在实验中,利用原子力显微镜可精确测量处理后的表面形貌,为优化预处理参数提供量化依据。研究还发现,表面预处理的均匀性对大面积晶圆键合尤为重要,团队据此改进了预处理设备的参数分布,使 6 英寸晶圆表面的活化程度更趋一致。这些细节上的优化,为提升晶圆键合的整体质量奠定了基础。山西晶圆级晶圆键合代工